In our previous blog (Part 1) we discussed various interface choices for die-to-die connections. We reviewed how parallel wires are beneficial for chiplet architecture in terms of latency, throughput, and power. Following the selection of a parallel wire interface, two main technologies for parallel interfaces have emerged the past few months, based on packaging choices and throughput requirements.

The first one, OHBI (Open HBI) is an initiative based on silicon interposer. It requires fine ubump pitches of 45-55um with dense signal pitches. This allows for Terabits of throughput between the two dies. OpenFive already announced both PHY and Controller solutions for this technology last year and this has picked up significant customer traction.

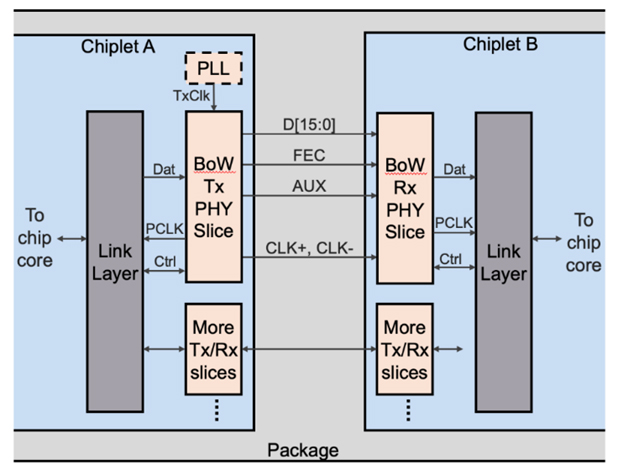

The second technology, BoW (Bunch of Wires) is an initiative based on an organic substrate. It supports C4 bumps (130-150um) on organic substrate. There are many new players supporting physical interface using BoW. More details about BoW interface can be found here. We will introduce OpenFive’s link layer controller in this blog and discuss the framing and protocol layer in some more detail.

"interface" - Google News

February 02, 2022 at 02:25PM

https://ift.tt/jn64P3fra

Interface Agnostic Universal D2D Controller for HPC and Chiplets (BoW): Part 2 - Design and Reuse

"interface" - Google News

https://ift.tt/eklz8Phir

https://ift.tt/46R2XH7Db

Bagikan Berita Ini

0 Response to "Interface Agnostic Universal D2D Controller for HPC and Chiplets (BoW): Part 2 - Design and Reuse"

Post a Comment