Over the years as microcontrollers have become fast enough to do the heavy lifting, we have become used to 10 megabit Ethernet being bit-banged from interfaces it was never meant to emerge from. We think however that we’ve never seen one driven from an SPI interface, so this one from [Ivan] may be a first. With a cleverly designed transceiver using logic chips, it even offers a chance to understand something about the timing of an Ethernet interface, too.

The differential logic signals derived from a simple Ethernet transceiver can be read by an SPI bus, but for the lack of a clock line. The challenge was then to construct a circuit the would construct the required clock pulses from the state changes on the data line. This would become a monostable with XOR gate, and a shift register to handle the clock during the preamble phase.

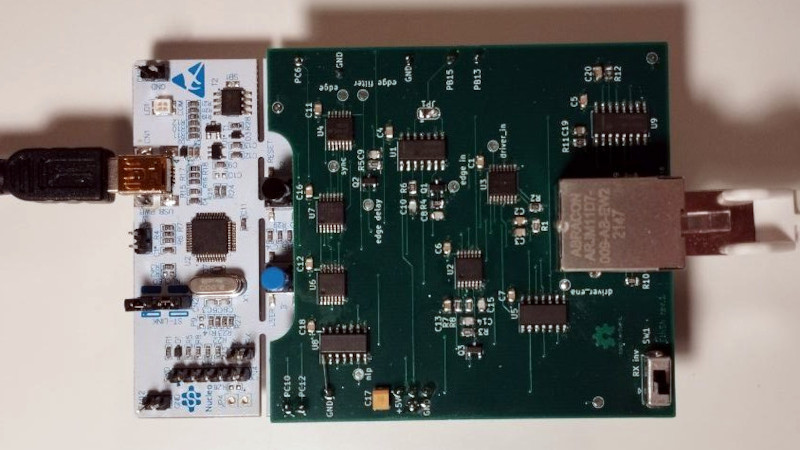

The resulting circuitry fits neatly on a shield for the ST Nucleo 64 board, where while it might not be the obvious choice for an Ethernet shield it certainly does the job.

If unexpected Ethernet is your thing, how about the i2s peripheral on an ESP8266?

"interface" - Google News

December 20, 2022 at 02:30AM

https://ift.tt/013g9kx

It's Ethernet, From An SPI Interface - Hackaday

"interface" - Google News

https://ift.tt/NTADnSt

https://ift.tt/E7oBnOa

Bagikan Berita Ini

0 Response to "It's Ethernet, From An SPI Interface - Hackaday"

Post a Comment